# Intel<sup>®</sup> Server Board SE7501WV2

**Technical Product Specification**

Intel reference number C25653-001

**Revision 1.0**

December 2002

**Enterprise Platforms and Services Division**

# Revision History

| Date  | Revision<br>Number | Modifications                                              |

|-------|--------------------|------------------------------------------------------------|

| 11/02 | 0.5                | First draft for internal review based on the SE7500WV2 TPS |

| 12/02 | 1.0                | Production Release                                         |

|       |                    |                                                            |

# **Disclaimers**

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

The Intel® Server Board SE7501WV2 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copyright © Intel Corporation 2003.

\*Other brands and names are the property of their respective owners.

# **Table of Contents**

| 1. | Introdu | uction                          | 17 |

|----|---------|---------------------------------|----|

| 2. | SE750   | 1WV2 Server Board Overview      | 18 |

| 2  | 2.1     | SE7501WV2 Feature Set           | 18 |

| 3. | Functi  | onal Architecture               | 21 |

| 3  | 3.1     | Processor and Memory Subsystem  | 21 |

|    | 3.1.1   | Processor Support               | 21 |

|    | 3.1.2   | Memory Subsystem                | 23 |

| 3  | 3.2     | Intel® E7501 Chipset            | 27 |

|    | 3.2.1   | MCH Memory Architecture         | 28 |

|    | 3.2.2   | MCH North Bridge                | 28 |

|    | 3.2.3   | P64H2                           | 29 |

|    | 3.2.4   | ICH3-S                          | 30 |

| 3  | 3.3     | Super I/O                       | 32 |

|    | 3.3.1   | GPIOs                           | 32 |

|    | 3.3.2   | Serial Ports                    | 33 |

|    | 3.3.3   | BIOS Flash                      | 37 |

| 4. | Config  | uration and Initialization      | 38 |

|    | 4.1.1   | Main Memory                     | 38 |

|    | 4.1.2   | Memory Shadowing                | 38 |

|    | 4.1.3   | System Management Mode Handling | 39 |

| 4  | 1.2     | I/O Map                         | 39 |

| 4  | 1.3     | Accessing Configuration Space   | 39 |

|    | 4.3.1   | CONFIG_ADDRESS Register         | 39 |

|    | 4.4    | Hardware Initialization                          | 41 |

|----|--------|--------------------------------------------------|----|

|    | 4.5    | Clock Generation and Distribution                | 41 |

|    | 4.6    | PCI I/O Subsystem                                | 44 |

|    | 4.6.1  | PCI Subsystem                                    | 44 |

|    | 4.6.2  | P32-A: 32-bit, 33-MHz PCI Subsystem              | 44 |

|    | 4.6.3  | P64-B and P64-C: 64-bit, 100-MHz PCI-X Subsystem | 45 |

|    | 4.7    | Ultra320 SCSI                                    | 47 |

|    | 4.8    | ATA-100                                          | 47 |

|    | 4.9    | Video Controller                                 | 48 |

|    | 4.9.1  | Video Modes                                      | 48 |

|    | 4.9.2  | Video Memory Interface                           | 49 |

|    | 4.9.3  | Front Panel Video Memory                         | 50 |

|    | 4.10   | Network Interface Controller (NIC)               | 50 |

|    | 4.10.1 | NIC Connector and Status LEDs                    | 50 |

|    | 4.11   | Interrupt Routing                                | 50 |

|    | 4.11.1 | Legacy Interrupt Routing                         | 51 |

|    | 4.11.2 | Serialized IRQ Support                           | 51 |

|    | 4.11.3 | APIC Interrupt Routing                           | 51 |

| 5. | Server | Management                                       | 54 |

|    | 5.1    | Sahalee Baseboard Management Controller (BMC)    | 55 |

|    | 5.1.1  | Fault Resilient Booting                          | 61 |

|    | 5.2    | System Reset Control                             | 62 |

|    | 5.2.1  | Power-up Reset                                   | 62 |

|    | 5.2.2  | Hard Reset                                       | 62 |

|    | 5.2.3  | Soft Reset                                       | 63 |

| į  | 5.3   | Intelligent Platform Management Buses (IPMB)                   | 63 |

|----|-------|----------------------------------------------------------------|----|

| į  | 5.4   | Inter Chassis Management Bus (ICMB)                            | 63 |

| į  | 5.5   | Error Reporting                                                | 64 |

|    | 5.5.1 | Error Sources and Types                                        | 64 |

|    | 5.5.2 | PCI Bus Errors                                                 | 64 |

|    | 5.5.3 | Intel <sup>®</sup> Xeon™ Processor Bus Errors                  | 64 |

|    | 5.5.4 | Memory Bus Errors                                              | 64 |

|    | 5.5.5 | Fault and Status LEDs                                          | 64 |

|    | 5.5.6 | Temperature Sensors                                            | 70 |

| 6. | BIOS  |                                                                | 71 |

| (  | 6.1   | System Flash ROM Layout                                        | 71 |

| 6  | 6.2   | BIOS Boot Specification Compliance                             | 71 |

| (  | 6.3   | Memory                                                         | 72 |

|    | 6.3.1 | Memory Configuration                                           | 73 |

|    | 6.3.2 | Memory Sizing and Initialization                               | 73 |

|    | 6.3.3 | ECC Initialization                                             | 74 |

|    | 6.3.4 | Memory Remapping                                               | 74 |

|    | 6.3.5 | DIMM Failure LED                                               | 74 |

| (  | 6.4   | Processors                                                     | 74 |

| 6  | 6.5   | Extended System Configuration Data (ESCD), Plug and Play (PnP) | 74 |

|    | 6.5.1 | Resource Allocation                                            | 75 |

|    | 6.5.2 | PnP ISA Auto-Configuration                                     | 75 |

|    | 6.5.3 | PCI Auto-Configuration                                         | 76 |

| 6  | 6.6   | NVRAM API                                                      | 76 |

| 6  | 6.7   | Legacy ISA Configuration                                       | 76 |

| 6.8    | Automatic Detection of Video Adapters             | 76 |

|--------|---------------------------------------------------|----|

| 6.9    | Keyboard / Mouse Configuration                    | 77 |

| 6.9.1  | Boot without Keyboard and/or Mouse                | 77 |

| 6.10   | Floppy Drives                                     | 77 |

| 6.11   | Universal Serial Bus (USB)                        | 78 |

| 6.12   | BIOS Supported Server Management Features         | 78 |

| 6.12.1 | IPMI                                              | 78 |

| 6.12.2 | Advanced Configuration and Power Interface (ACPI) | 79 |

| 6.12.3 | Wake Events                                       | 80 |

| 6.12.4 | Front Panel Switches                              | 80 |

| 6.12.5 | Wired For Management (WFM)                        | 81 |

| 6.12.6 | PXE BIOS Support                                  | 82 |

| 6.12.7 | BIOS Recommendations                              | 82 |

| 6.13   | Console Redirection                               | 82 |

| 6.13.1 | Operation                                         | 83 |

| 6.13.2 | Keystroke Mappings                                | 83 |

| 6.13.3 | Limitations                                       | 86 |

| 6.14   | Emergency Management Port (EMP)                   | 87 |

| 6.14.1 | Serial Ports                                      | 87 |

| 6.14.2 | Interaction with BIOS Console Redirection         | 87 |

| 6.15   | Service Partition Boot                            | 87 |

| 6.16   | System Management BIOS (SMBIOS)                   | 88 |

| 6.17   | Microsoft* Windows* Compatibility                 | 90 |

| 6.17.1 | Quiet Boot                                        | 91 |

| 6.18   | BIOS Serviceabilty Features                       | 91 |

| 6.18.1 | CMOS Reset                       | 91  |

|--------|----------------------------------|-----|

| 6.19   | BIOS Updates                     | 92  |

| 6.19.1 | Flash Update Utility             | 92  |

| 6.19.2 | Loading the System BIOS          | 93  |

| 6.19.3 | User Binary Area                 | 93  |

| 6.19.4 | BIOS Recovery Mode               | 93  |

| 6.19.5 | Rolling BIOS and On-line updates | 94  |

| 6.20   | BIOS and System Setup            | 95  |

| 6.20.1 | BIOS Setup Utility               | 95  |

| 6.20.2 | Setup Utility Operation          | 96  |

| 6.21   | BIOS Security Features           | 109 |

| 6.21.1 | Operating Model                  | 109 |

| 6.22   | Password Protection              | 110 |

| 6.23   | Inactivity Timer                 | 111 |

| 6.24   | Hot Key Activation               | 111 |

| 6.25   | Password Clear Jumper            | 111 |

| 6.26   | Secure Mode (Unattended start)   | 111 |

| 6.27   | Front Panel Lock                 | 111 |

| 6.28   | Video Blanking                   | 111 |

| 6.29   | PS/2 Keyboard and Mouse Lock     | 112 |

| 6.30   | Secure Boot (Unattended Start)   | 112 |

| 6.31   | Error Handling                   | 112 |

| 6.31.1 | Error Sources and Types          | 112 |

| 6.32   | SMI Handler                      | 113 |

| 6.33   | PCI Bus Error                    | 113 |

| ( | 5.34   | Processor Bus Error                         | . 113 |

|---|--------|---------------------------------------------|-------|

| 6 | 6.35   | Single-Bit ECC Error Throttling Prevention  | . 113 |

| 6 | 6.36   | System Limit Error                          | . 114 |

| 6 | 6.37   | Boot Event                                  | . 114 |

| ( | 5.38   | Fault Resilient Booting (FRB)               | . 114 |

|   | 6.38.1 | FRB3                                        | . 114 |

|   | 6.38.2 | FRB2                                        | . 114 |

| ( | 5.39   | Boot Monitoring                             | . 116 |

|   | 6.39.1 | Purpose                                     | . 116 |

| ( | 6.40   | Logging Format Conventions                  | . 118 |

|   | 6.40.1 | Memory Error Events                         | . 118 |

|   | 6.40.2 | PCI Error Events                            | . 120 |

|   | 6.40.3 | FRB-2 Error Events                          | . 121 |

| 6 | 6.41   | POST Codes, Error Messages, and Error Codes | . 122 |

|   | 6.41.1 | POST Progress Code LEDs                     | . 122 |

|   | 6.41.2 | POST Error Codes and Messages               | . 123 |

|   | 6.41.3 | POST Error Beep Codes                       | . 125 |

|   | 6.41.4 | BIOS Recovery Beep Codes                    | . 125 |

|   | 6.41.5 | Bootblock Error Beep Codes                  | . 126 |

| ( | 6.42   | "POST Error Pause" Option                   | . 127 |

| ( | 5.43   | SE7501WV2 Server Board BIOS Runtime APIs    | . 127 |

| ( | 6.44   | INT 15 Extensions                           | . 127 |

|   | 6.44.1 | Cache Services                              | . 127 |

|   | 6.44.2 | Intel ID String                             | . 128 |

|   | 6.44.3 | Processor Information                       | . 129 |

|    | 6.44.4           | Extended NVRAM Services                                                    | . 129 |

|----|------------------|----------------------------------------------------------------------------|-------|

|    | 6.44.5           | IPMB Services                                                              | . 130 |

|    | 6.44.6<br>Master | INT15h, Function DA20h, Subfunction 99h/9Ah/9Bh – Read/Write/Bus Write IMB | . 130 |

| 6  | 6.45             | Multiple Processor Support (MPS)                                           | . 130 |

|    | 6.45.1           | Multiprocessor Specification Support                                       | . 130 |

|    | 6.45.2           | Multiple Processor Support                                                 | . 131 |

|    | 6.45.3           | Mixed Processor Support                                                    | . 131 |

| 6  | 6.46             | Hyper-Threading Technology                                                 | . 132 |

| 6  | 6.47             | OEM Customization                                                          | . 132 |

| 6  | 6.48             | User Binary                                                                | . 132 |

|    | 6.48.1           | Scan Point Definitions                                                     | . 134 |

|    | 6.48.2           | Format of the User Binary Information Structure                            | . 135 |

|    | 6.48.3           | OEM Splash Screen                                                          | . 135 |

|    | 6.48.4           | Localization                                                               | . 135 |

| 7. | SE750            | 1WV2 ACPI Implementation                                                   | 136   |

| 7  | 7.1              | ACPI                                                                       | . 136 |

|    | 7.1.1            | Front Panel Switches                                                       | . 136 |

|    | 7.1.2            | Wake up Sources (ACPI and Legacy)                                          | . 138 |

| 8. | SE750            | 1WV2 Connectors                                                            | 139   |

| 8  | 3.1              | Power Connectors                                                           | . 139 |

| 8  | 3.2              | Memory Module Connector                                                    | . 140 |

| 8  | 3.3              | Processor Socket                                                           | . 141 |

| 3  | 3.4              | System Management Headers                                                  | . 143 |

|    | 8.4.1            | ICMB Header                                                                | . 143 |

|    | 8.4.2            | OEM IPMB Header                                                            | . 143 |

| 8       | 3.5                                                                                    | PCI I/O Riser Slot Connector                                                                                                                                                                                               | 143                                |

|---------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 8       | 3.6                                                                                    | Front Panel Connectors                                                                                                                                                                                                     | 146                                |

|         | 8.6.1                                                                                  | High Density 100-Pin Floppy / Front Panel / IDE Connector (J2G1)                                                                                                                                                           | 148                                |

|         | 8.6.2                                                                                  | VGA Connector                                                                                                                                                                                                              | 150                                |

|         | 8.6.3                                                                                  | SCSI Connectors                                                                                                                                                                                                            | 150                                |

|         | 8.6.4                                                                                  | NIC Connector                                                                                                                                                                                                              | 151                                |

|         | 8.6.5                                                                                  | ATA RAID Connectors                                                                                                                                                                                                        | 152                                |

|         | 8.6.6                                                                                  | USB Connector                                                                                                                                                                                                              | 153                                |

|         | 8.6.7                                                                                  | Floppy Connector                                                                                                                                                                                                           | 154                                |

|         | 8.6.8                                                                                  | Serial Port Connector                                                                                                                                                                                                      | 155                                |

|         | 8.6.9                                                                                  | Keyboard and Mouse Connector                                                                                                                                                                                               | 155                                |

| 8       | 3.7                                                                                    | Miscellaneous Headers                                                                                                                                                                                                      | 156                                |

|         | 8.7.1                                                                                  | For Hondon                                                                                                                                                                                                                 | 156                                |

|         | 0.7.1                                                                                  | Fan Headers                                                                                                                                                                                                                | 150                                |

| 9.      |                                                                                        | uration Jumpers                                                                                                                                                                                                            |                                    |

|         |                                                                                        |                                                                                                                                                                                                                            | 157                                |

| Ç       | Config                                                                                 | uration Jumpers                                                                                                                                                                                                            | <b>157</b><br>157                  |

| 9       | <b>Config</b><br>9.1<br>9.2                                                            | System Recovery and Update Jumpers                                                                                                                                                                                         | <b>157</b><br>157<br>158           |

| 9<br>10 | Config<br>9.1<br>9.2<br>. Genera                                                       | uration Jumpers  System Recovery and Update Jumpers  External RJ45 Serial Port Jumper Block                                                                                                                                | 157<br>157<br>158<br>159           |

| ;<br>10 | Config<br>9.1<br>9.2<br>. Genera                                                       | uration Jumpers  System Recovery and Update Jumpers  External RJ45 Serial Port Jumper Block  Specifications                                                                                                                | 157 157 158159 159                 |

| ;<br>10 | Config<br>9.1<br>9.2<br>. Genera<br>10.1                                               | System Recovery and Update Jumpers  External RJ45 Serial Port Jumper Block  Al Specifications  Absolute Maximum Ratings                                                                                                    | 157 158 159 159 159                |

| 9<br>10 | Config<br>9.1<br>9.2<br>. Genera<br>10.1                                               | System Recovery and Update Jumpers  External RJ45 Serial Port Jumper Block  Al Specifications  Absolute Maximum Ratings  Power Information                                                                                 | 157 157 158159 159 159 159         |

| 9<br>10 | Config<br>9.1<br>9.2<br>. Genera<br>10.1<br>10.2                                       | System Recovery and Update Jumpers  External RJ45 Serial Port Jumper Block  Al Specifications  Absolute Maximum Ratings  Power Information  SE7501WV2 Server Board Power Budget                                            | 157 158 159 159 159 160            |

| 9<br>10 | Config<br>9.1<br>9.2<br>. Genera<br>10.1<br>10.2<br>10.2.1<br>10.3<br>10.3.1           | System Recovery and Update Jumpers  External RJ45 Serial Port Jumper Block  Al Specifications  Absolute Maximum Ratings  Power Information  SE7501WV2 Server Board Power Budget  Power Supply Specifications               | 157157158159159159159160           |

| 9       | Config<br>9.1<br>9.2<br>. Genera<br>10.1<br>10.2<br>10.2.1<br>10.3<br>10.3.1<br>10.3.2 | System Recovery and Update Jumpers  External RJ45 Serial Port Jumper Block  Al Specifications  Absolute Maximum Ratings  Power Information  SE7501WV2 Server Board Power Budget  Power Supply Specifications  Power Timing | 157 157 158159 159 159 160 160 163 |

| 11.1.1     | Product Safety Compliance                                              | . 164 |

|------------|------------------------------------------------------------------------|-------|

| 11.1.2     | Product EMC Compliance                                                 | . 164 |

| 11.1.3     | Product Regulatory Compliance Markings                                 | . 164 |

| 11.2       | Electromagnetic Compatibility Notices                                  | . 165 |

| 11.2.1     | Europe (CE Declaration of Conformity)                                  | . 165 |

|            | Australian Communications Authority (ACA) (C-Tick Declaration of mity) | . 165 |

|            | Ministry of Economic Development (New Zealand) Declaration of mity     | . 165 |

| 11.2.4     | BSMI (Taiwan)                                                          | . 165 |

| 11.3       | Replacing the Back up Battery                                          | . 165 |

| 12. Mecha  | nical Specifications                                                   | 167   |

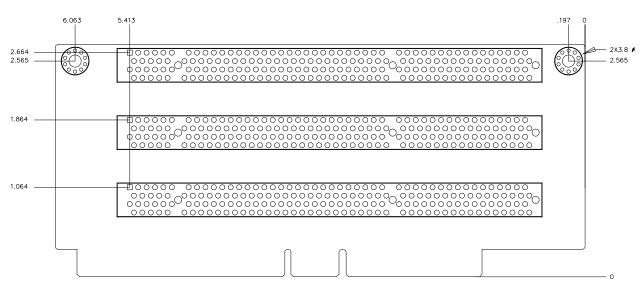

| 12.1       | PCI Riser Cards                                                        | . 168 |

| 12.1.1     | 1-Slot 3.3V PCI Riser Card                                             | . 168 |

| 12.1.2     | 3-Slot 3.3V PCI Riser Card                                             | . 168 |

| Appendix A | A: Glossary                                                            | 169   |

# **List of Figures**

| Figure 1. Intel <sup>®</sup> Server Board SE7501WV2 Block Diagram                 | 20  |

|-----------------------------------------------------------------------------------|-----|

| Figure 2. Memory Sub-system Block Diagram                                         | 24  |

| Figure 3. Memory Bank Label Definition                                            | 26  |

| Figure 4. Serial Port Mux Logic                                                   | 35  |

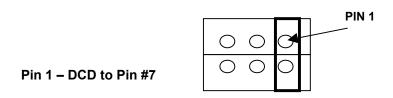

| Figure 5. J5A2 Jumper Block for DCD Signal                                        | 36  |

| Figure 6. J5A2 Jumper Block for DSR Signal                                        | 36  |

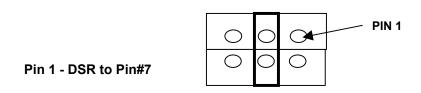

| Figure 7. CONFIG_ADDRES Register                                                  | 40  |

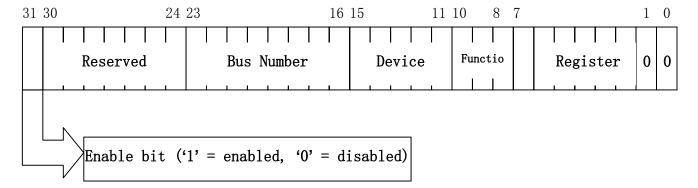

| Figure 8. Intel <sup>®</sup> Server Board SE7501WV2 Clock Distribution            | 43  |

| Figure 9. Intel <sup>®</sup> Server Board SE7501WV2 Sahalee BMC Block Diagram     | 54  |

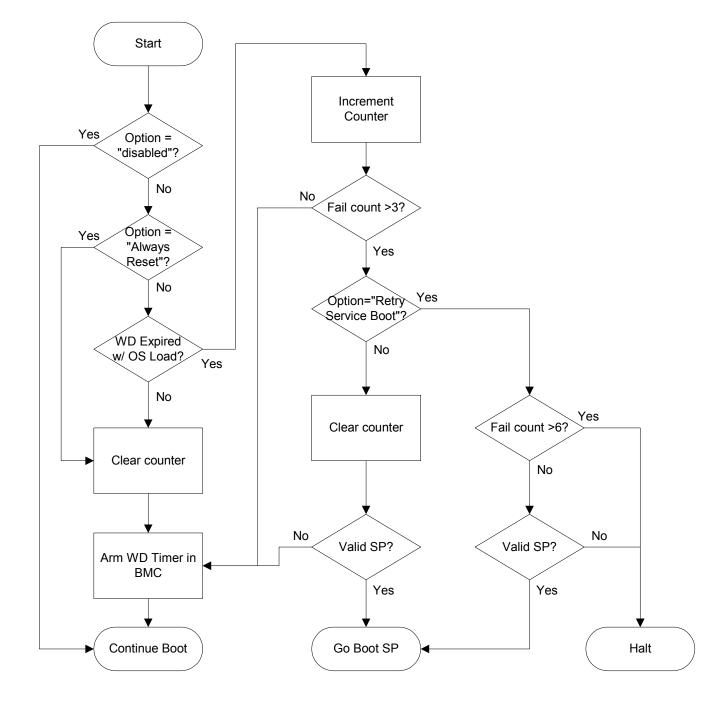

| Figure 10. BIOS Boot Monitoring Flowchart                                         | 117 |

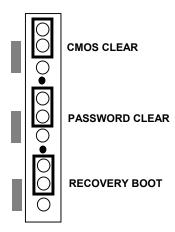

| Figure 11. Intel <sup>®</sup> Server Board SE7501WV2 Configuration Jumpers (J1D4) | 157 |

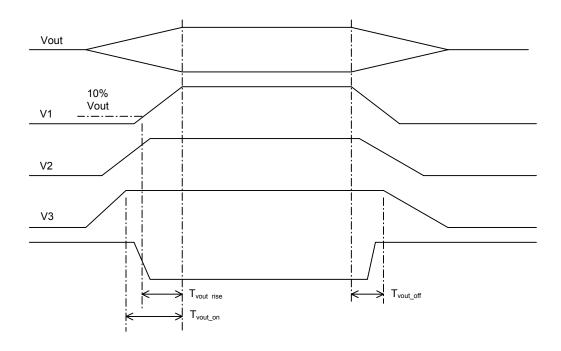

| Figure 12. Output Voltage Timing                                                  | 161 |

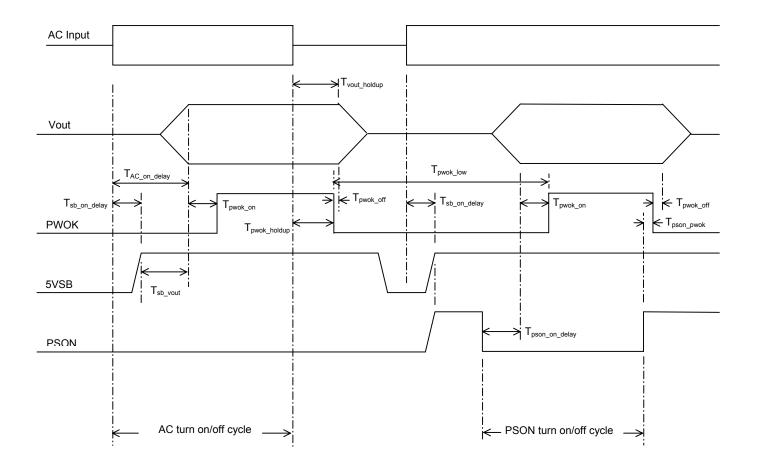

| Figure 13. Turn On / Off Timing                                                   | 162 |

| Figure 14. Intel <sup>®</sup> Server Board SE7501WV2 Mechanical Drawing           | 167 |

| Figure 15. 1-Slot PCI Riser Mechanical Drawing                                    | 168 |

| Figure 16. 3-Slot PCI Riser Mechanical Drawing                                    | 168 |

# **List of Tables**

| Table 1. Intel® Server Board SE7501WV2 Processor Support Matrix for 533MHz | 21 |

|----------------------------------------------------------------------------|----|

| Table 2. Intel® Server Board SE7501WV2 Processor Support Matrix for 400MHz | 22 |

| Table 3. Memory Bank Labels                                                | 25 |

| Table 4. P64-B Speeds                                                      | 29 |

| Table 5. P64-C Speeds                                                      | 30 |

| Table 6. Super I/O GPIO Usage Table                                        | 32 |

| Table 7. Serial A Header Pin-out                                           | 34 |

| Table 8. Rear Serial Port B Adapter Pinout                                 | 36 |

| Table 9. PCIdevice IDs                                                     | 40 |

| Table 10. PCI Bus Segment Characteristics                                  | 44 |

| Table 11. P32-A Configuration IDs                                          | 44 |

| Table 12. P32-Arbitration Connections                                      | 45 |

| Table 13. P64-B Configuration IDs                                          | 45 |

| Table 14. P64-C Configuration IDsIDs                                       | 45 |

| Table 15. P64-B Arbitration Connections                                    | 46 |

| Table 16. P64-C Arbitration Connections                                    | 46 |

| Table 17. Video Modes                                                      | 49 |

| Table 18. Video Memory Interface                                           | 49 |

| Table 19. Interrupt Definitions                                            | 51 |

| Table 20. Intel® Server Board SE7501WV2 Interrupt Mapping                  | 52 |

| Table 21. BMC Pinout                                                       | 55 |

| Table 22. ADM1026 Input Definition                                         | 60 |

| Table 23. Intel® Server Board SE7501WV2 I2C Address Map                    | 63 |

| Table 24. System Status LEDs                                               | 65 |

| Table 25. Boot Block POST Progress Codes                                   | 67 |

| Table 26. Allowed Combinations of Floppy Drive and Floppy Media            | 77 |

| Table 27. Supported Wake Events                                            | 80 |

| Table 28. Non-ASCII Key Mappings                                           | 84 |

| Table 29. ASCII Key Mappings                                               | 86 |

| Table 30. SMBIOS Header Structure                                          | 89 |

| Table 31. Setup Utility Screen                                    | 97  |

|-------------------------------------------------------------------|-----|

| Table 32. Keyboard Command Bar                                    | 97  |

| Table 33. Main Menu Selections                                    | 99  |

| Table 34. Primary Master and Slave Adapters Sub-menu Selections   | 100 |

| Table 35. Processor Settings Sub-menu                             | 100 |

| Table 36. Advanced Menu Selections                                | 101 |

| Table 37. Advanced Chipset Control Sub-menu Selections            | 101 |

| Table 38. PCI Configuration Sub-menu Selections                   | 101 |

| Table 39. PCI Device, Embedded Devices                            | 102 |

| Table 40. I/O Device/Peripheral Configuration Sub-menu Selections | 102 |

| Table 41. Memory Configuration Menu Selections                    | 103 |

| Table 42. Security Menu Selections                                | 103 |

| Table 43. Server Menu Selections                                  | 104 |

| Table 44. System Management Sub-menu Selections                   | 105 |

| Table 45. Serial Console Redirection Sub-menu Selections          | 106 |

| Table 46. Event Log Configuration Sub-menu Selections             | 106 |

| Table 47. Fault Resilient Boot Sub-menu Selections                | 107 |

| Table 48. Boot Menu Selections                                    | 107 |

| Table 49. Boot Device Priority Selections                         | 107 |

| Table 50. Hard Drive Selections                                   | 108 |

| Table 51. Removable Devices Selections                            | 108 |

| Table 52. Exit Menu Selections                                    | 108 |

| Table 53. Security Features Operating Model                       | 109 |

| Table 54. Memory Error Event Data Field Contents                  | 119 |

| Table 55. PCI Error Event Data Field Contents                     | 120 |

| Table 56. Examples of Event Data Field Contents for PCI Errors    | 121 |

| Table 57. FRB-2 Event Data Field Contents                         | 121 |

| Table 58. Examples of Event Data Field Contents for FRB-2 Errors  | 122 |

| Table 59. POST Progress Code LED Example                          | 123 |

| Table 60. Standard POST Error Messages and Codes                  | 123 |

| Table 61. Extended POST Error Messages and Codes                  | 124 |

| Table 62. BIOS Recovery Beep Codes                                | 125 |

| Table 63. Bootblock Error Beep Codes                              | 126 |

| Table 64. Three-beep Boot Block Memory Failure Error Codes                     | . 126 |

|--------------------------------------------------------------------------------|-------|

| Table 65. Interrupt 15h Extensions                                             | . 127 |

| Table 66. User Binary Area Scan Point Definitions                              | . 134 |

| Table 67. User Binary Information Structure                                    | . 135 |

| Table 68. Supported Wake Events                                                | . 138 |

| Table 69. Power Connector Pin-out (J3J1)                                       | . 139 |

| Table 70. Power Supply Signal Connector (J1J1)                                 | . 139 |

| Table 71. 12V Power Connector (J4J1)                                           | . 139 |

| Table 72. DIMM Connectors (J5F1, J5F2, J5F3, J6F1, J6F2, J6F3)                 | . 140 |

| Table 73. Socket 604 Processor Socket Pinout                                   | . 141 |

| Table 74. ICMB Header Pin-out (J9B2)                                           | . 143 |

| Table 75. IPMB Header Pin-out (J9C1)                                           | . 143 |

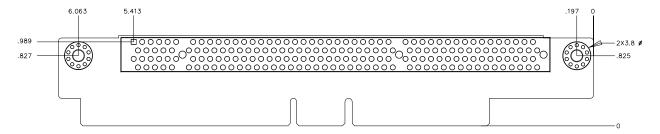

| Table 76. P64-B Full Length PCI Riser Slot Pin-out                             | . 143 |

| Table 77. P64-C Low-Profile Riser Slot Pin-out                                 | . 144 |

| Table 78. 34-pin Front Panel Connector Signal Descriptions                     | . 146 |

| Table 79. SSI Compliant 24-pin Front Panel Connector Pinout (J1H1)             | . 148 |

| Table 80. High density 100-Pin Floppy/Front Panel/IDE Connector Pin out (J2G1) | . 148 |

| Table 81. VGA Connector Pin-out (J8A1)                                         | . 150 |

| Table 82. 68-pin VHDCI SCSI and Wide Connectors Pin-out (J7B1, J7A1)           | . 150 |

| Table 83. Stacked Dual RJ-45 Connector Pin-out (JA6A1)                         | . 151 |

| Table 84. ATA-100 RAID 40-pin Connectors Pin-out (J1D1, J1D2)                  | . 152 |

| Table 85. ATA-100 Legacy 40-pin Connector Pinout (J1G2)                        | . 153 |

| Table 86. USB Connectors Pin-out (J4A1, J9A1)                                  | . 153 |

| Table 87. Optional USB Connection Header Pin-out (J1D3)                        | . 154 |

| Table 88. Legacy 34-pin Floppy Connector Pin-out (J1G1)                        | . 154 |

| Table 89. Rear Low-Profile RJ-45 Serial B Port Pin-out (J5A1)                  | . 155 |

| Table 90. 9-pin Header Serial A Port Pin-out (J9A2)                            | . 155 |

| Table 91. Keyboard and Mouse PS/2 Connector Pin-out (J6A1)                     | . 156 |

| Table 92. Three-pin Fan Headers Pin-out (J4J2, J7J1)                           | . 156 |

| Table 93. Fan Pack Fan Header Pin-out (J3J2)                                   | . 156 |

| Table 94. Configuration Jumper Options                                         | . 157 |

| Table 95. Absolute Maximum Ratings                                             | . 159 |

| Table 96. Intel® Server Board SE7501WV2/SR2300/SR1300 Power Budget             | . 159 |

| Table 97. Intel <sup>®</sup> Server Board SE7501WV2 Static Power Supply Voltage Spec | ification160 |

|--------------------------------------------------------------------------------------|--------------|

| Table 98. Intel <sup>®</sup> Server Board SE7501WV2 Dynamic Power Supply Voltage     |              |

| Specification                                                                        | 160          |

| Table 99. Voltage Timing Parameters                                                  | 161          |

| Table 100. Turn On / Off Timing                                                      | 161          |

# 1. Introduction

The Intel® SE7501WV2 server board Technical Product Specification (TPS) provides a high-level technical description for the Intel® SE7501WV2 server board. It details the architecture and feature set for all functional sub-systems that make up the server board.

This document is sub-divided into the following main categories:

Chapter 2: SE7501WV2 Server Board Overview

**Chapter 3:** Functional Architecture

Chapter 4: Configuration and Initialization

**Chapter 5:** Server Management

Chapter 6: BIOS

Chapter 7: SE7501WV2 Server Board ACPI Implementation

Chapter 8: SE7501WV2 Server Board Connectors

**Chapter 9**: Configuration Jumpers

**Chapter 10:** General Specifications

**Chapter 11:** Regulatory and Integration Information

**Chapter 12:** Mechanical Specification

The contents of this document are derived from several of the SE7501WV2's External Product Specifications (EPS). For a more detailed, lower level description of a particular functional subsystem, the EPS for the sub-system should be ordered from your Intel field representative. The EPS documents available for the SE7501WV2 server board include the following:

- Intel<sup>®</sup> SE7501WV2 server board BIOS EPS

- Intel<sup>®</sup> SE7501WV2 server board Baseboard Management Controller EPS

- Sahalee Core BMC EPS for IPMI v1.5 System

The SE7501WV2 server board supports the Intel® Server Management Version 5.5 software. One additional EPS document is available to provide technical detail on the feature set of the server management software. This document is:

ISM Customization EPS

# 2. SE7501WV2 Server Board Overview

The SE7501WV2 server board is a monolithic printed circuit board with features that were designed to support the high-density 1U and 2U server market.

# 2.1 SE7501WV2 Feature Set

Two different SE7501WV2 server boards will be made available. One will provide an embedded Ultra-320\* SCSI interface and the other will provide an embedded ATA-100\* "Value-Raid" interface. Both boards support the following feature set:

- Dual Intel<sup>®</sup> Xeon<sup>™</sup> processor in the Socket 604 INT3/FCPGA package

- 533 MHz Front Side Bus

- Intel<sup>®</sup> E7501 chipset

- E7501 North Bridge

- P64H2 I/O Bridge

- ICH3-S South Bridge

- Support for up to six DDR266 compliant registered ECC DIMMs providing up to 12 GB of memory, when 2G DIMMs become available and have been tested. (Will support DDR200 modules when 400MHz processors are installed.)

- Three separate and independent PCI buses:

- Segment A: 32-bit, 33 MHz, 5 V (P32-A) with two embedded devices:

- 2D/3D graphics controller: ATI Rage\* XL Video Controller with 8 MB of memory

- ATA-100 controller: Promise Technology\* PDC20277 (ATA-100 board only)

- Segment B: 64-bit, 133 MHz, 3.3 V, PCI-X (P64-B) supporting the following configuration:

- One PCI I/O riser slot capable of supporting full length PCI add-in cards

- Dual-channel Intel® 10/100/1000 82546EB Gigabit Ethernet Controller

- Segment C: 64-bit, 133 MHz, 3.3 V PCI-X (P64-C) supporting the following devices:

- One PCI I/O riser slot capable of supporting low-profile PCI add-in cards

- Dual-channel SCSI with Zero Channel RAID (ZCR) and host RAID support (SCSI SKU only)

- LPC (Low Pin Count) bus segment with two embedded devices:

- Platform Management Controller (PMC) providing monitoring, alerting, and logging of critical system information obtained from embedded sensors on the server board

- Super I/O controller chip providing all PC-compatible I/O (floppy, serial, keyboard, mouse)

- X-Bus segment with one embedded device:

- Flash ROM device for system BIOS: Intel® 32-megabit 28F320C3 Flash ROM

- Two external Universal Serial Bus (USB) ports with an additional internal header providing two optional USB ports for front panel support

- One external low-profile RJ45 serial port. An internal header is also available providing an optional serial port.

- One IDE connector, supporting one or two ATA-100 compatible devices

- Support for up to seven system fans

- Fault/Status LEDs throughout the server board

- Multiple server management headers providing on-board interconnects to server management features

- SSI-compliant connectors for SSI interface support: front panel, floppy, and ATA-33

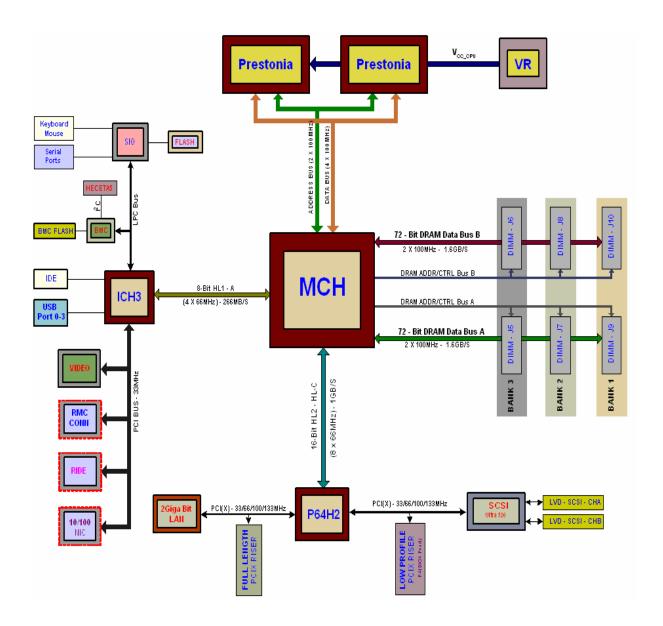

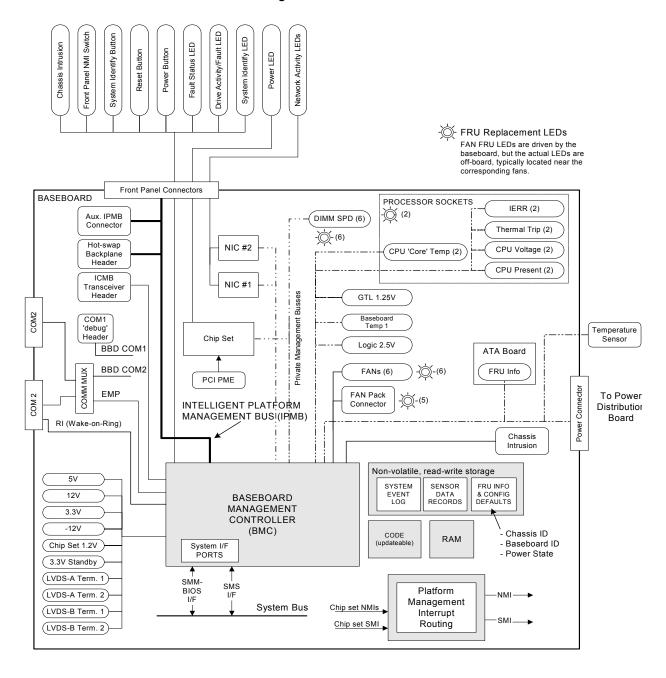

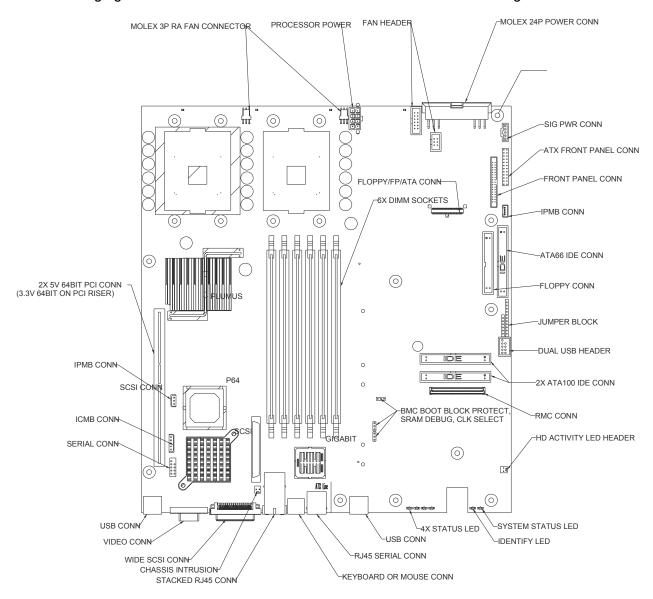

Figure 1 shows the functional blocks of the server board and the plug-in modules that it supports.

Figure 1. Intel® Server Board SE7501WV2 Block Diagram

# 3. Functional Architecture

This chapter provides a high-level description of the functionality distributed between the architectural blocks of the SE7501WV2 server board.

# 3.1 Processor and Memory Subsystem

The E7501 chipset provides a 36-bit address, 64-bit data processor host bus interface, operating at 400MHz and 533Mz in the AGTL+ signaling environment. The MCH component of the chipset provides an integrated memory controller, an 8-bit Hub Interface, and three 16-bit Hub Interfaces.

The Hub Interface provides the interface to two 64-bit, 133-MHz, Rev 1.0 compliant PCI-X buses via the P64H2. The SE7501WV2 server board directly supports up to 12 GB of ECC memory, using six DDR266 compliant registered ECC DIMMs. (Will support DDR200 modules when 400MHz processors are installed.) The ECC implementation in the MCH can detect and correct single-bit errors, detect multiple-bit errors, and support the Intel® Single Device Data Correction features.

# 3.1.1 Processor Support

The SE7501WV2 server board supports one or two Intel<sup>®</sup> Xeon<sup>™</sup> processors in the Socket 604 INT3/FCPGA package. When two processors are installed, all processors must be of identical revision, core voltage, and bus/core speed. When only one processor is installed, it should be in the socket labeled CPU-1 and the other socket must be empty. The support circuitry on the server board consists of the following:

- Dual Socket 604 INT3/FCPGA CPU sockets supporting 533 MHz (will support 400 MHz processors running at 400 Mhz speed.)

- Processor host bus AGTL+ support circuitry

Table 1. Intel® Server Board SE7501WV2 Processor Support Matrix for 533MHz

| Speed (MHz)<br>533MHz | Product Code    | MM#    | Test<br>Specification<br>(S-spec) | Stepping | CPUID | L2<br>Cache<br>Size | Notes |

|-----------------------|-----------------|--------|-----------------------------------|----------|-------|---------------------|-------|

| 2.8 GHz (1U)          | BX80532KE2800DU | 851292 | SL6GG                             | C1       | 0F24  | 512k                | 1     |

| 2.8 GHz (1U)          | BX80532KE2800DU | 851275 | SL6NS                             | C1       | 0F24  | 512k                | 1     |

| 2.8 GHz               | BX80532KE2800D  | 851275 | SL6NS                             | C1       | 0F24  | 512k                | 1     |

| 2.8gGHz               | BX80532KE2800D  | 851285 | SL6GG                             | C1       | 0F24  | 512k                | 1     |

| 2.66 GHz (1U)         | BX80532KE2667DU | 851650 | SL6GF                             | C1       | 0F24  | 512k                | 1     |

| 2.66 GHz (1U)         | BX80532KE2667DU | 851713 | SL6NR                             | C1       | 0F24  | 512k                | 1     |

| 2.66 GHz              | BX80532KE2667D  | 851647 | SL6GF                             | C1       | 0F24  | 512k                | 1     |

| 2.66 GHz              | BX80532KE2667D  | 851712 | SL6GF                             | C1       | 0F24  | 512k                | 1     |

| 2.4 GHz (1U)          | BX80532KE2400DU | 851290 | SL6GD                             | C1       | 0F24  | 512k                | 1     |

| 2.4 GHz (1U)          | BX80532KE2400DU | 851273 | SL6NQ                             | C1       | 0F24  | 512k                | 1     |

| 2.4 GHz               | BX80532KE2400D  | 851280 | SL6GD                             | C1       | 0F24  | 512k                | 1     |

| 2.4 GHz               | BX80532KE2400D  | 851269 | SL6NQ                             | C1       | 0F24  | 512k                | 1     |

| 2.0 GHz (1U)          | BX80532KE2000DU | 851288 | SL6RQ                             | C1       | 0F24  | 512k                | 1     |

| 2.0 GHz (1U)          | BX80532KE2000DU | 851272 | SL6NP                             | C1       | 0F24  | 512k                | 1     |

| 2.0 GHz               | BX80532KE2000D  | 851279 | SL6NP                             | C1       | 0F24  | 512k                | 1     |

| 2.0 GHz               | BX80532KE2000D  | 851268 | SL6NP                             | C1       | 0F24  | 512k                | 1     |

Test L2 Speed (MHz) **Product Code** MM# Specification Stepping **CPUID** Cache **Notes** 400MHz (S-spec) Size 2.8 GHz BX80532KC2800D 850007 SL6MS 0F24 512k 2.8 GHz 80532KC072512 849546 SL6M7 C1 0F24 512k 1 2.8GHz (1U) BX80532KC2800DU 850614 SL6M7 C1 0F24 512k 1 BX80532KC2600D C1 2.6 GHz 0F24 512k 1 850609 SL6EQ 0F24 2.6 GHz 80532KC064512 C1 512k 847694 SL6EQ 1 BX80532KC2600DU 0F24 2.6 GHz (1U) 849701 C1 512k 1 SL6EQ 2.4 GHz BX80532KC2400D 845163 **SL687** tB0 0F24 512k 1 2.4 GHz 80532KC056512 847695 SL6EP C1 0F24 512k 1 2.4 GHz BX80532KC2400D 0F24 512k 851738 SL6EP C<sub>1</sub> 1 2.4 GHz (1U) BX80532KC2400DU 849703 SL6K2 B<sub>0</sub> 0F24 512k 2.2 GHz BX80532KC2200D 843623 SL624 tB0 0F24 512k 1 2.2 GHz 80532KC049512 SL6JZ 0F24 512k 849112 C1 1 BX80532KC2200D 0F24 512k 2.2 GHz 49356 SL6JZ C1 1 BX80532KC2200DU 0F24 2.2 GHz (1U) 848431 SL624 tB0 512k 1 0F24 BX80532KC2000D 2.0 GHz 843637 SL623 tB0 512k 1 2.0 GHz 80532KC041512 849063 SL6JY C1 0F24 512k 1 1.8 GHz BX80532KC1800D tB0 0F24 512k 843620 SL622 1 1.8 GHz 80532KC033512 SL6JX 0F24 512k 849064 C1 1 1.8 GHz (1U) BX80532KC1800DU 848419 SL622 tB0 0F24 512k 1

Table 2. Intel® Server Board SE7501WV2 Processor Support Matrix for 400MHz

**Notes:** Processors must be populated in sequential order. That is, CPU socket #1 must be populated before CPU socket #2.

- The SE7501WV2 server board is designed to provide up to 75 A per processor.

Processors with higher current requirements are not supported.

- Processor terminators are not required in unpopulated processor sockets.

In addition to the circuitry described above, the processor subsystem contains the following:

- Processor module presence detection logic

- Server management registers and sensors

## 3.1.1.1 Processor VRM

The SE7501WV2 baseboard has a single VRM (Voltage Regulator Module) to support two processors. It is compliant with the VRM 9.1 specification and provides a maximum of 150 AMPs, which is capable of supporting currenlyt supported processors as well as those supported in the future.

The board hardware and BMC must read the processor VID (voltage identification) bits for each processor before turning on the VRM. If the VIDs of the two processors are not identical, then the BMC will not turn on the VRM and a beep code is generated.

# 3.1.1.2 Reset Configuration Logic

The BIOS determines the processor stepping, cache size, etc through the CPUID instruction. The requirements are that all processors in the system must operate at the same frequency, have the same cache sizes, and have the same VID. No mixing of product families is supported.

On the SE7501WV2 platform, the BIOS is responsible for configuring the processor speeds. The processor information is read at every system power-on. The speed is set to correspond to the speed of the slowest processor installed.

**Note:** No manual processor speed setting options exist either in the form of a BIOS setup option or jumpers when using production level processors.

#### 3.1.1.3 Processor Module Presence Detection

Logic is provided on the baseboard to detect the presence and identity of installed processors. The BMC checks the logic and will not turn on the system DC power unless the VIDs of both processors match in a dual processor configuration.

# 3.1.1.4 Interrupts and APIC

Interrupt generation and notification to the processors is done by the APICs in the ICH3 and the P64H2 using messages on the front side bus.

## 3.1.1.5 Server Management Registers and Sensors

The Baseboard Management Controller manages registers and sensors associated with the processor / memory subsystem. For more information, refer to Section 5.

# 3.1.2 Memory Subsystem

The SE7501WV2 server board supports up to six DIMM slots for a maximum memory capacity of 12 GB. The DIMM organization is x72, which includes eight ECC check bits. The memory interface runs at 266MHz. (200MHz when DDR200 DRAM's and 400MHz processors are used.)

The memory controller supports memory scrubbing, single-bit error correction, multiple-bit error detection, and the Intel® Single Device Data Correction feature. Memory can be implemented with either single sided (one row) or double-sided (two row) DIMMs.

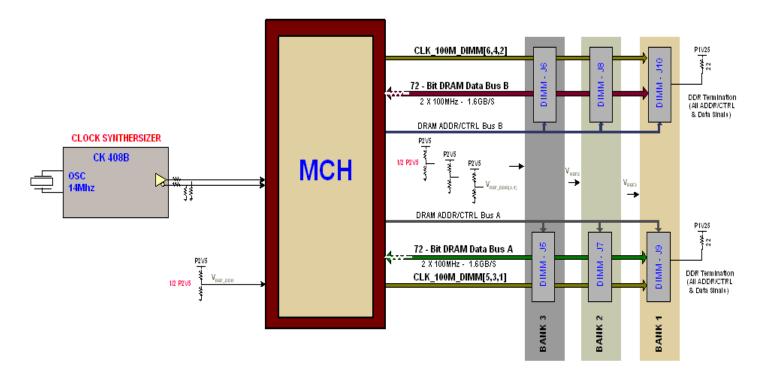

The following figure provides a block diagram of the memory sub-system implemented on the SE7501WV2 server board.

Figure 2. Memory Sub-system Block Diagram

# 3.1.2.1 Memory DIMM Support

The SE7501WV2 server board supports DDR266 compliant registered ECC DIMMs operating at 266MHz. (DDR200 DIMMs are supported when 400MHz processors are used.)

Only DIMMs tested and qualified by Intel or a designated memory test vendor are supported on the SE7501WV2 server board. A list of tested DIMMs will be made available. Note that all DIMMs are supported by design, but only fully tested DIMMs will be supported.

The minimum supported DIMM size is 128 MB. Therefore, the minimum main memory configuration is 2 x 128 MB or 256 MB. The largest size DIMM supported is a 2 GB stacked registered DDR266 ECC DIMM based on 512 megabit technology. (DDR200 DIMMs are supported when 400MHz processors are used)

Only registered DDR266 compliant, ECC, DDR memory DIMMs will be supported. (DDR200 DIMMs are supported when 400MHz processors are used.)

- ECC single-bit errors will be corrected and multiple-bit errors will be detected. The SE7501WV2 server board also supports the Intel® Single Device Data Correction feature.

- The maximum memory capacity is 12 GB.

- The minimum memory capacity is 256 MB.

# 3.1.2.2 Memory Configuration

The memory interface between the MCH and DIMMs is 144 bits wide. This requires that two DIMMs be populated per bank in order for the system to operate. At least one bank has to be

populated in order for the system to boot. If additional banks have less than two DIMMs, the memory for that bank(s) will not be available to the system.

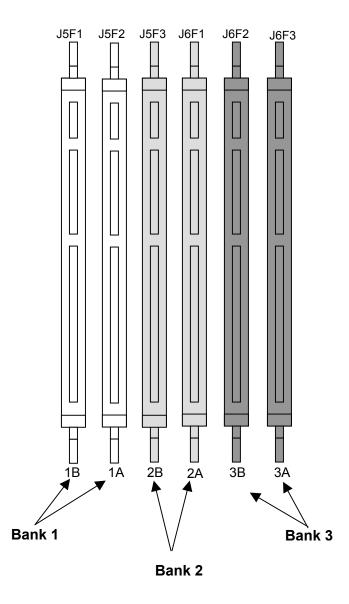

There are three banks of DIMMs, labeled 1, 2, and 3. Bank 1 contains DIMM locations 1A and 1B, Bank 2 contains 2A and 2B, and Bank 3 contains 3A and 3B. DIMM socket identifiers are marked with silkscreen next to each DIMM socket on the baseboard. Note that the sockets associated with any given bank are located next to each other.

Certain combinations of DIMM types in the same system can violate the write Ringback measurement specification during analog validation.

• When mixing double-ranked DIMMs (x4 or x8) with single-ranked DIMMs (x4 or x8), if a single-ranked DIMM is placed in the populated slot closest to the MCH, the Write Ringback at that DIMM violates the JEDEC DRAM specification.

The baseboard's signal integrity and cooling are optimized when memory banks are populated in order. Therefore, when installing memory, DIMMs should be installed starting with Bank 1 and ending with Bank 3.

DIMM and memory configurations must adhere to the following:

- DDR266 registered ECC DIMM modules (DDR200 when 400MHz processors are used)

- DIMM organization: x72 ECC

- Pin count: 184

- DIMM capacity: 128 MB, 256 MB, 512 MB, 1 GB, 2 GB

- Serial PD: JEDEC Rev 2.0

- Voltage options: 2.5 V (VDD/VDDQ)

- Interface: SSTL2

- Two DIMMs must be populated in a bank for a x144 wide memory data path.

- Any or all memory banks may be populated.

Table 3. Memory Bank Labels

| Memory DIMM                    | Bank |

|--------------------------------|------|

| J5F1 (DIMM 1B), J5F2 (DIMM 1A) | 1    |

| J5F3 (DIMM 2B), J6F1 (DIMM 2A) | 2    |

| J6F2 (DIMM 3B), J6F3 (DIMM 3A) | 3    |

Figure 3. Memory Bank Label Definition

# 3.1.2.3 I<sup>2</sup>C\*Bus

An I<sup>2</sup>C\* bus connects the six DIMM slots to the ICH3-S and the BMC. This bus is used by the system BIOS to retrieve DIMM information needed to program the MCH memory registers which are required to boot the system.

# 3.1.2.4 DIMM Failure LED

The SE7501WV2 server board provides DIMM Failure LEDs located next to each DIMM slot on the baseboard. The DIMM Failure LEDs are used to indicate double-bit DIMM errors. If a

double-bit error is detected during POST, the BIOS sends a Set DIMM State command to the BMC indicating that the DIMM LED is lit.

# 3.1.2.5 Intel® Single Device Data Correction feature

The SE7501WV2 server board supports Intel's Single Device Data Correction correct memory architecture, which gives the memory sub-system the ability to withstand a multi-bit failure within a DRAM device, including a failure that causes incorrect data on all data bits of the device.

# 3.2 Intel® E7501 Chipset

The SE7501WV2 server board is designed around the Intel® E7501 chipset. The chipset provides an integrated I/O bridge and memory controller, and a flexible I/O subsystem core (PCI-X). This is targeted for multiprocessor systems and standard high-volume servers. The Intel E7501 chipset consists of three components:

- MCH: Memory Controller Hub North Bridge. The MCH North Bridge accepts access requests from the host (processor) bus and directs those accesses to memory or to one of the PCI buses. The MCH monitors the host bus, examining addresses for each request. Accesses may be directed to a memory request queue for subsequent forwarding to the memory subsystem, or to an outbound request queue for subsequent forwarding to one of the PCI buses. The MCH also accepts inbound requests from the P64H2 and the ICH3-S. The MCH is responsible for generating the appropriate controls to control data transfer to and from memory.

- **P64H2: PCI-X 64bit Hub 2.0 I/O Bridge.** The P64H2 provides the interface for two 64-bit, 133MHz Rev. 1.0 compliant PCI-X buses. The P64H2 is both master and target on both PCI-X buses.

- ICH3-S: South Bridge. The ICH3-S controller has several components. It provides the interface for a 32-bit, 33-MHz Rev. 2.2-compliant PCI bus. The ICH3-S can be both a master and a target on that PCI bus. The ICH3-S also includes a USB controller and an IDE controller. The ICH3-S is also responsible for much of the power management functions, with ACPI control registers built in. The ICH3-S also provides a number of GPIO pins and has the LPC bus to support low speed legacy I/O.

The MCH, P64H2, and ICH3-S chips provide the pathway between processor and I/O systems. The MCH is responsible for accepting access requests from the host (processor) bus, and directing all I/O accesses to one of the PCI buses or legacy I/O locations. If the cycle is directed to one of the 64-bit PCI segments, the MCH communicates with the P64H2 through a private interface called the HI (Hub Interface). If the cycle is directed to the ICH3-S, the cycle is output on the MCH's 8bit HI 1.5 bus. The P64H2 translates the HI 2.0 bus operation to a 64-bit PCI-X Rev. 1.0-compliant signaling environment operating from 100MHz to 133 MHz. The ICH3-S translates the HI 1.5 bus operation to a 32-bit PCI Rev. 2.2-compliant signaling environment operating at 33MHz.

The HI 2.0 bus is 16 bits wide and operates at 66 MHz with 512MT/s, providing over 1 GB per second of bandwidth.

All I/O for the SE7501WV2 server board, including PCI and PC-compatible I/O, is directed through the MCH and then through either the P64H2 or the ICH3-S provided PCI buses.

- The ICH3-S provides a 32-bit/33-MHz PCI bus hereafter called P32-A.

- The P64H2 provides two independent 64-bit, 133-MHz PCI-X buses hereafter called P64-B, and P64-C.

This independent bus structure allows all three PCI buses to operate concurrently.

# 3.2.1 MCH Memory Architecture

The MCH supports a 144-bit wide Memory Sub-system that can support a maximum of 12 GB (using 2 GB DIMMs). This configuration needs external registers for buffering the memory address and control signals. In this configuration the MCH supports six DDR266 compliant registered stacked DIMMs for a maximum of 12 GB. (DDR200 DIMMs are supported when 400MHz processors are used.) The six chip selects are registered inside the MCH and need no external registers for chip selects.

The memory interface runs at 266 MHz. (200 MHz when DDR-200 modules and 400 MHz processors are used.) The memory interface supports a 144-bit wide memory array. It uses fifteen address lines (BA[1:0] and MA[12:0]) and supports 64 Mb, 128 Mb, 256 Mb, 512 Mb DRAM densities. The DDR DIMM interface supports memory scrubbing, single-bit error correction, and multiple bit error detection as well as the Intel® Single Device Data Correction features.

# 3.2.1.1 DDR Configurations

The DDR interface supports up to 12GB of main memory and supports single- and double-density DIMMs.

# 3.2.2 MCH North Bridge

The E7501 MCH North Bridge (MCH) is a 1005 ball FC-BGA device and uses the proven components of previous generations like the Intel® Pentium® 4 bus interface unit, the Hub Interface unit, and the DDR memory interface unit. In addition, the MCH incorporates a Hub Interface (HI). The hub interface enables the MCH to directly interface with the P64H2. The MCH also increases the main memory interface bandwidth and maximum memory configuration with a 144-bit wide memory interface.

The MCH integrates three main functions:

- An integrated high performance main memory subsystem.

- An HI 2.0 bus interface that provides a high-performance data flow path between the host bus and the I/O subsystem.

- A HI 1.5 bus which provides an interface to the ICH3-S (South Bridge).

Other features provided by the MCH include the following:

- Full support of ECC on the memory bus

- Full support of the Intel® Single Device Data Correction features.

- Twelve deep in-order queue

- Full support of registered DDR266 ECC DIMMs (DDR200 DIMMs when 400MHz processors are used)

- Support for 12 GB of DDR memory

- Memory scrubbing

# 3.2.3 P64H2

The P64H2 is a 567-ball FCBGA device and provides an integrated I/O bridge that provides a high-performance data flow path between the HI 2.0 and the 64-bit I/O subsystem. This subsystem supports peer 64-bit PCI-X segments. Because it has two PCI interfaces, the P64H2 can provide large and efficient I/O configurations. The P64H2 functions as the bridge between the HI and the two 64-bit PCI-X I/O segments. The HI can support 1 GB/s of data bandwidth.

## 3.2.3.1 PCI Bus P64-B I/O Subsystem

The P64-B supports the following embedded devices and connectors:

- One 184-pin, 5-volt keyed, 64-bit PCI expansion slot connector. The expansion slot can be used for either a 1-slot or a 3-slot PCI riser card. Both riser cards support 184-pin, 3.3V keyed, 64-bit PCI expansion slots. The PCI slots on the P64-B PCI bus support both full-length PCI cards and low profile PCI cards with the appropriate faceplate.

- One Intel® 82546EB dual channel 10/100/1000 Ethernet controller.

The BIOS is responsible for setting the bus speed of the P64-B. The following tables show the bus frequency according to slot population. The bus speed will always be set up to run at the speed of the slowest card installed.

| Configuration                                          | Intel <sup>®</sup> Server Chassis <b>SR1300</b> (Bus B with Anvik* Dual NIC down and 1 Slot Riser) | Intel <sup>®</sup> Server Chassis SR2300<br>(Bus B with Anvik* Dual NIC<br>down and 3 Slot Riser) |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Adapter Cards installed and on board device enabled    | PCI-X 64/100                                                                                       | PCI-X 64/100                                                                                      |

| Adapter Cards installed and on board device enabled    | PCI-X 64/100                                                                                       | PCI-X 64/100                                                                                      |

| 2 Adapter Cards installed and on board device enabled  | N/A                                                                                                | PCI-X 64/100                                                                                      |

| 3 Adapter Cards installed and on board device enabled  | N/A                                                                                                | PCI-X 64/66                                                                                       |

| Adapter Cards installed and on board device disabled   | PCI-X 64/100                                                                                       | PCI-X 64/100                                                                                      |

| 2 Adapter Cards installed and on board device disabled | N/A                                                                                                | PCI-X 64/100                                                                                      |

| 3 Adapter Cards installed and on board device disabled | N/A                                                                                                | PCI-X 64/66                                                                                       |

Table 4. P64-B Speeds

## 3.2.3.2 PCI Bus P64-C I/O Subsystem

P64-C supports the following embedded devices and connectors:

- One 184-pin, 5-volt keyed, 64-bit PCI expansion slot connector. The expansion slot can be used for either a 1-slot or a 3-slot PCI riser card. Both riser cards support 184-pin, 3.3V keyed, 64-bit PCI expansion slots. The PCI slots on the P64-C PCI bus support only low profile PCI cards.

- One Adaptec\* 7902 dual channel U-320 SCSI controller.

• Support for Zero Channel RAID (ZCR) or M-ROMB that allows the on board SCSI controller to be "hidden" from system and used by the RAID processor on the add-in card.

The BIOS is responsible for setting the bus speed of the P64-C. The bus speed will always be set up to run at the speed of the slowest card installed.

Intel<sup>®</sup> Server Chassis **SR1300** Intel® Server Chassis SR2300 Configuration (Bus C with AIC7902 SCSI down (Bus C with AIC7902 SCSI and 1 Slot Riser) down and 3 Slot Riser) 0 Adapter Cards installed and on board device PCI-X 100 PCI-X 100 enabled 1 Adapter Cards installed PCI-X 100 PCI-X 100 and on board device enabled 2 Adapter Cards installed and on board device N/A PCI-X 100 enabled 3 Adapter Cards installed PCI-X 64/66 and on board device N/A enabled 1 Adapter Cards installed and on board device PCI-X 64/100 PCI-X 64/100 disabled 2 Adapter Cards installed and on board device N/A PCI-X 64/100 disabled 3 Adapter Cards installed and on board device N/A PCI-X 64/66 disabled

Table 5. P64-C Speeds

# 3.2.4 ICH3-S

The ICH3-S is a multi-function device, housed in a 421-pin BGA device, providing a HI 1.5 to PCI bridge, a PCI IDE interface, a PCI USB controller, and a power management controller. Each function within the ICH3-S has its own set of configuration registers. Once configured, each appears to the system as a distinct hardware controller sharing the same PCI bus interface.

On the SE7501WV2 server board, the primary role of the ICH3-S is to provide the gateway to all PC-compatible I/O devices and features. The SE7501WV2 server board uses the following ICH3-S features:

- PCI bus interface

- LPC bus interface

- IDE interface, with Ultra DMA 100 capability

- Universal Serial Bus (USB) interface

- PC-compatible timer/counter and DMA controllers

- APIC and 8259 interrupt controller

- Power management

- System RTC

- General purpose I/O

The following are the descriptions of how each supported feature is used on the SE7501WV2 server board.

## 3.2.4.1 PCI Bus P32-A I/O Subsystem

The ICH3-S provides a legacy 32-bit PCI subsystem and acts as the central resource on this PCI interface. The P32-A supports the following embedded devices and connectors:

- An ATI\* Rage XL video controller with 3D/2D graphics accelerator

- Promise Technology\* PDC20277 dual channel ATA-100 controller (ATA-100 board only)

#### 3.2.4.2 PCI Bus Master IDE Interface

The ICH3-S acts as a PCI-based Ultra DMA/100 IDE controller that supports programmed I/O transfers and bus master IDE transfers. The ICH3-S supports two IDE channels, supporting two drives each (drives 0 and 1). The SE7501WV2 server board provides two separate interfaces to the IDE controller. The first is a single SSI compliant 40-pin (2x20) IDE connector. The second is through the high-density 100-pin floppy / IDE / front panel connector that is used with the Intel® SR1300 and SR2300 server chassis.

The SE7501WV2 IDE interface supports Ultra DMA/100 Synchronous DMA Mode transfers on the 40-pin connector and supports Ultra DMA/33 transfers on the 100-pin connector.

## 3.2.4.3 USB Interface

The ICH3-S contains three USB controllers and six USB ports. The USB controller moves data between main memory and the six USB ports. All six ports function identically and with the same bandwidth. The SE7501WV2 server board only supports four of the six ports on the board.

The SE7501WV2 provides two external USB ports on the back of the server board. The first external connector is located within the standard ATX I/O panel area while the second is located directly behind the P64-B full-length PCI card slot. The USB specification defines the external connectors.

The third and fourth USB ports are optional and can be accessed by cabling from the internal 9-pin connector located on the baseboard to external USB ports located either in the front or the rear of a given chassis.

# 3.2.4.4 Compatibility Interrupt Control

The ICH3-S provides the functionality of two 82C59 PIC devices for ISA-compatible interrupt handling.

## 3.2.4.5 APIC

The ICH3-S integrates an APIC that is used to distribute 24 interrupts.

# 3.2.4.6 Power Management

One of the embedded functions of the ICH3-S is a power management controller. The SE7501WV2 server board uses this to implement ACPI-compliant power management features. The SE7501WV2 supports sleep states S0, S1, S4, and S5.

# 3.3 Super I/O

The National Semiconductor\* PC87417 Super I/O device contains all of the necessary circuitry to control two serial ports, one parallel port, one floppy disk, and one PS/2-compatible keyboard and mouse. The SE7501WV2 server board supports the following features:

- GPIOs

- Two serial ports

- Floppy

- Keyboard and mouse through one PS/2 connector

- Wake up control

#### 3.3.1 **GPIOs**

The National Semiconductor\* PC87417 Super I/O provides nine general-purpose input/output pins that the SE7501WV2 server board utilizes. The following table identifies the pin and the signal name used in the schematic:

Table 6. Super I/O GPIO Usage Table

| Pin | Name            | IO/GPIO   | Intel <sup>®</sup> Server Board<br>SE7501WV2 Use |

|-----|-----------------|-----------|--------------------------------------------------|

| 124 | GPIO00/CLKRUN_L | I/O       | TP                                               |

| 125 | GPIO01/KBCLK    | I/O       | KB_CLK                                           |

| 126 | GPIO02/KBDAT    | I/O       | KB_DAT                                           |

| 127 | GPIO03/MCLK     | I/O       | MS_CLK                                           |

| 128 | GPIO04/MDAT     | I/O       | MS_DAT                                           |

| 9   | GPIO05/XRDY     | I/O       | TP                                               |

| 10  | GPIO06/XIRQ     | I/O       | BMC_SYSIRQ                                       |

| 13  | GPIO07/HFCKOUT  | I/O       | SIO_CLK_40M_BMC                                  |

| 1   | GPIOE10/XA11    | I/O,I(E)1 | XBUS_A<11>                                       |

| 2   | GPIOE11/XA10    | I/O,I(E)1 | XBUS_A<10>                                       |

| 3   | GPIOE12/XA9     | I/O,I(E)1 | XBUS_A<9>                                        |

| 4   | GPIOE13/XA8     | I/O,I(E)1 | XBUS_A<8>                                        |

| 5   | GPIOE14/XA7     | I/O,I(E)1 | XBUS_A<7>                                        |

| 6   | GPIOE15/XA6     | I/O,I(E)1 | XBUS_A<6>                                        |

| 7   | GPIOE16/XA5     | I/O,I(E)1 | XBUS_A<5>                                        |

| Pin | Name                 | IO/GPIO   | Intel <sup>®</sup> Server Board<br>SE7501WV2 Use |

|-----|----------------------|-----------|--------------------------------------------------|

| 8   | GPIOE17/XA4          | I/O,I(E)1 | XBUS_A<4>                                        |

| 14  | GPIO20/XRD_XEN_L     | I/O       | XBUS_XRD_L                                       |

| 15  | GPIO21/XWR_XRW_L     | I/O       | XBUS_XWR_L                                       |

| 16  | GPIO22/XA3           | I/O       | XBUS_A<3>                                        |

| 17  | GPIO23/XA2           | I/O       | XBUS_A<2>                                        |

| 18  | GPIO24/XA1           | I/O       | XBUS_A<1>                                        |

| 19  | GPIO25/XA0           | I/O       | XBUS_A<0>                                        |

| 22  | GPIO26/XCS1_L        | I/O       | TP                                               |

| 23  | GPIO27/XCS0_L        | I/O       | XBUS_XCS0_L                                      |

| 24  | GPIO30/XD7           | I/O       | XBUS_D<7>                                        |

| 25  | GPIO31/XD6           | I/O       | XBUS_D<6>                                        |

| 26  | GPIO32/XD5           | I/O       | XBUS_D<5>                                        |

| 27  | GPIO33/XD4           | I/O       | XBUS_D<4>                                        |

| 28  | GPIO34/XD3           | I/O       | XBUS_D<3>                                        |

| 29  | GPIO35/XD2           | I/O       | XBUS_D<2>                                        |

| 30  | GPIO36/XD1           | I/O       | XBUS_D<1>                                        |

| 31  | GPIO37/XD0           | I/O       | XBUS_D<0>                                        |

| 20  | GPIOE40/XCS3_L       | I/O,I(E)1 | TP                                               |

| 21  | GPIOE41/XCS2_L       | I/O,I(E)1 | TP                                               |

| 35  | GPIOE42/SLBTIN_L     | I/O,I(E)1 | TP                                               |

| 49  | GPIOE43/PWBTOUT_L    | I/O,I(E)1 | ZZ_POST_CLK_LED_L                                |

| 50  | GPIOE44/LED1         | I/O,I(E)1 | ZZ_BIOS_ROLLING                                  |

| 51  | GPIOE45/LED2         | I/O,I(E)1 | FP_PWR_LED_L                                     |

| 52  | GPIOE46/SLPS3_L      | I/O,I(E)1 | TP                                               |

| 53  | GPIOE47/SLPS5_L      | I/O,I(E)1 | TP                                               |

| 36  | GPIO50/PWBTN_L       | I/O       | TP                                               |

| 37  | GPIO51/SIOSMI_L      | I/O       | TP                                               |

| 38  | GPIO52/SIOSCI_L      | I/O       | SIO_PME_L                                        |

| 45  | GPIO53/LFCKOUT/MSEN0 | I/O       | TP                                               |

| 54  | GPIO54/VDDFELL       | I/O       | ZZ_POST_DATA_LED_L                               |

| 56  | GPIO55/CLKIN         | I/O       | CLK_48M_SIO                                      |

| 32  | GPO60/XSTB2/XCNF2_L  | 0         | PU_XBUS_XCNF2                                    |

| 33  | GPO61/XSTB1/XCNF1_L  | 0         | XBUS_XSTB1_L                                     |

| 34  | GPO62/XSTB0/XCNF0_L  | 0         | PU_XBUS_XCNF0                                    |

| 48  | GPO63/ACBSA          | 0         | PU_SIO_ACBSA                                     |

| 55  | GPO64/WDO_L/CKIN48   | 0         | PU_SIO_CKIN48                                    |

# 3.3.2 Serial Ports

The SE7501WV2 server board provides two serial ports: an external low-profile RJ45 Serial port, and an internal Serial header. The following sections provide details on the use of the serial ports.

## 3.3.2.1 Serial Port A

Serial A is an optional port, accessed through a 9-pin internal header (J9A2). A standard DH-10 to DB9 cable can be used to direct Serial A out the back of a given chassis. The Serial A interface follows the standard RS232 pin-out. The baseboard has a Serial Port A silkscreen label next to the connector as well as a location designator of J9A2. The Serial A connector is located next to the P64-C low-profile PCI card slot. A standard DH-10 to DB9 cable is available from Intel Corporation in the SE7501WV2 Serial Port Accessory Kit.

| Pin | Signal Name | Serial Port A Header Pin-out |  |

|-----|-------------|------------------------------|--|

| 1   | DCD         |                              |  |

| 2   | DSR         | 1 0 0 2                      |  |

| 3   | RX          | 3 0 0 4                      |  |

| 4   | RTS         | ]                            |  |

| 5   | TX          | 1 5 0 0 6                    |  |

| 6   | CTS         | 7   0 0  8                   |  |

| 7   | DTR         | 9 0                          |  |

| 8   | RI          | ]                            |  |

| 9   | GND         | 7                            |  |

Table 7. Serial A Header Pin-out

## 3.3.2.2 Serial Port B

Serial B is an external low profile 8-pin RJ45 connector that is located on the back of the board. For those server applications that require an external modem, an RJ45-to-DB9 adapter is necessary. A standard DH-10 to DB9 cable is available from Intel in the SE7501WV2 Serial Port Accessory Kit.

# 3.3.2.3 Serial Port Multiplexer Logic

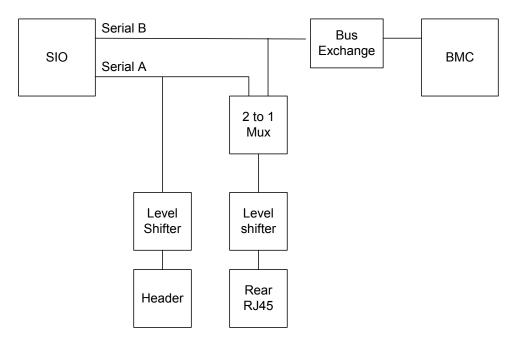

The SE7501WV2 server board has a multiplexer to connect the rear RJ45 connector to either Serial Port A or Serial Port B in both the Intel® Server Chassis SR1300 and SR2300. This facilitates the routing of Serial Port A to the rear RJ45 connector if Serial Port B is used for SOL (Serial Over LAN) in both the SR1300 and SR2300 server chassis. This serial port selection can be done through the BIOS setup option.

The following figure shows the serial port mux functionality.

Figure 4. Serial Port Mux Logic

#### 3.3.2.3.1 Rear RJ45 Serial B Port

The rear RJ45 Serial B port is a fully functional serial port that can support any standard serial device. Using an RJ45 connector for a serial port allows direct support for serial port concentrators, which typically use RJ45 connectors and are widely used in the high-density server market. For server applications that use a serial concentrator to access the server management features of the baseboard, a standard 8-pin CAT-5 cable from the serial concentrator is plugged directly into the rear RJ45 serial port.